#### 16-bit Serial-In/Parallel-Out Constant-Current LED Driver

#### **Product Description**

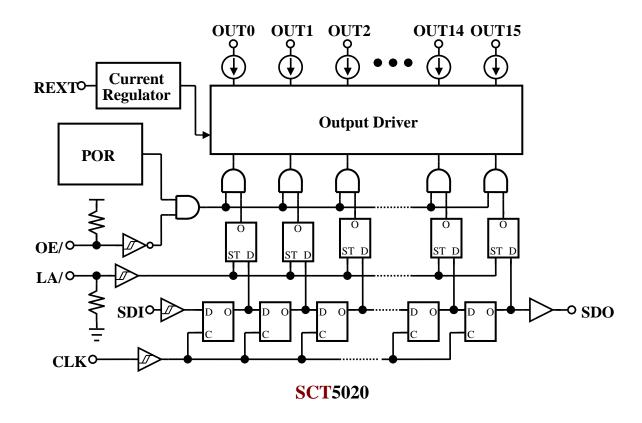

The SCT5020 serial-interfaced LED driver sinks 16 LED clusters with constant current to keep the uniform intensity of LED displays. In applications, an external resistor is used to set the full-scale constant output current from 1mA up to 45mA. The SCT5020 guarantees each output can endure maximum 17V DC voltage stress. The built-in shift registers and data latches making the SCT5020 effective solution in driving LED display. The output enable function gates all 16 outputs on and off, and is fast enough to be used as PWM input for LED intensity control. Since the serial data input rate can be reached up to 25MHz, the SCT5020 will satisfy system which needs high volume data transmission to control the LED display. Furthermore, the SCT5020 provides excellent temperature regulation thus it can be applied to varied of operating temperature. The SCT5020 built-in output pre-charge function which improves the picture quality of LED display.

#### **Features**

- Built-in output pre-charge function.

- Finest grayscale response with 40ns PWM pulse width

- 16 robust constant current sinker with LED power-supply voltage up to 17V

- Constant output current: 1 30/45mA@3.3/5V

- ♦ Wide power supply voltages: 3.3V to 5V

- Excellent regulation to load, supply voltage and temperature

Load regulation: ±0.1%/V Line regulation: ±0.5%/V

- High current matching accuracy: ±1% between outputs, ±2% between ICs

- Dropout voltage 0.5V@20mA, VDD=5V

- CMOS Schmitt trigger inputs with clock rate up to 25MHz @ cascade connection

- The constant current value of 16 outputs is set by a single external resistor

- ♦ Built-in power on reset(POR) circuit forces all the outputs off while power on

- ESD protection ability: HBM > 7KV, MM > 350V

- Package: SSOP24, SSOP24-1, SOP24 and TQFN24

- Applications: LED Displays, Variable Message Signs, Illumination, LED Traffic Signs

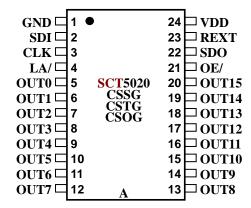

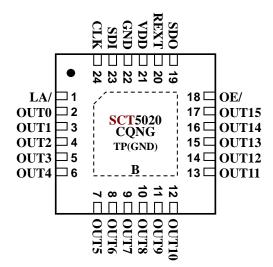

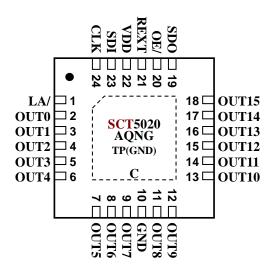

#### **Pin Configurations**

#### **Terminal Description**

| Pin Name  |      | Pin No.    |              | 1/0 | Frantian                                                                                                                  |

|-----------|------|------------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------|

|           | Α    | В          | С            | I/O | Function                                                                                                                  |

| GND       | 1    | 22<br>(TP) | 10<br>(TP)   | -   | Ground terminal(thermal pad included)                                                                                     |

| SDI       | 2    | 23         | 23           | I   | Serial input of data shift register.                                                                                      |

| CLK       | 3    | 24         | 24           | I   | Clock input of shift register, data is sampled at the rising edge of CLK.                                                 |

| LA/       | 4    | 1          | 1            | ı   | Input terminal of data strobe. Data is latched when LA/ is low. And data on shift register goes through when LA/ is high. |

| OUT[0:15] | 5-20 | 2-17       | 2-9<br>11-18 | 0   | Open-drain, constant-current outputs.                                                                                     |

| OE/       | 21   | 18         | 20           | I   | Output enable signal. Output is enabled when OE/ is forced to low.                                                        |

| SDO       | 22   | 19         | 19           | 0   | Output terminal of serial-data output to the SDI of next SCT5020.                                                         |

| REXT      | 23   | 20         | 21           | I/O | Used to connect an external resistor for setting up all output current                                                    |

| VDD       | 24   | 21         | 22           | -   | Supply voltage terminal                                                                                                   |

## **Block Diagram**

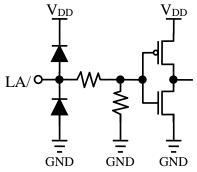

#### **Equivalent Circuits of Inputs (1)**

# OE/ OE/ GND

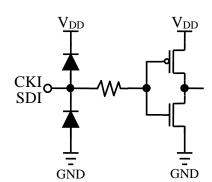

**Equivalent Circuits of Inputs (2)**

# **Equivalent Circuits of Inputs (3)**

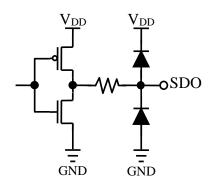

# **Equivalent Circuits of Output**

## **Ordering Information**

| Part        | Marking     | Package        | Unit per reel(pcs) |

|-------------|-------------|----------------|--------------------|

| SCT5020CSSG | SCT5020CSSG | Green SSOP24   | 2500               |

| SCT5020CSTG | SCT5020CSTG | Green SSOP24-1 | 2000               |

| SCT5020CSOG | SCT5020CSOG | Green SOP24    | 1000               |

| SCT5020CQNG | 5020CQNG    | Green TQFN24   | 3000               |

| SCT5020AQNG | 5020AQNG    | Green TQFN24   | 3000               |

#### StarChips Technology, Inc.

5F, No.5, Technology Rd., Science-Based Industrial Park, Hsin-Chu, Taiwan, R.O.C.

Tel: +886-3-577-5767 Ext.555, Fax: +886-3-577-6575,

E-mail: <a href="mailto:service@starchips.com.tw">service@starchips.com.tw</a>

#### **Truth Table**

| CLK     | LA/ | OE/ | SDI              | OUT0 ~ OUT15                                                          | SDO               |

|---------|-----|-----|------------------|-----------------------------------------------------------------------|-------------------|

|         | Н   | L   | Dn               | D <sub>n</sub> D <sub>n-1</sub> D <sub>n-14</sub> D <sub>n-15</sub>   | D <sub>n-15</sub> |

|         | L   | L   | D <sub>n+1</sub> | No change                                                             | D <sub>n-14</sub> |

|         | Н   | L   | D <sub>n+2</sub> | D <sub>n+2</sub> D <sub>n+1</sub> D <sub>n-12</sub> D <sub>n-13</sub> | D <sub>n-13</sub> |

| <b></b> | Х   | L   | D <sub>n+3</sub> | D <sub>n+2</sub> D <sub>n+1</sub> D <sub>n-12</sub> D <sub>n-13</sub> | D <sub>n-13</sub> |

| ₹       | Х   | Н   | D <sub>n+3</sub> | Off                                                                   | D <sub>n-13</sub> |

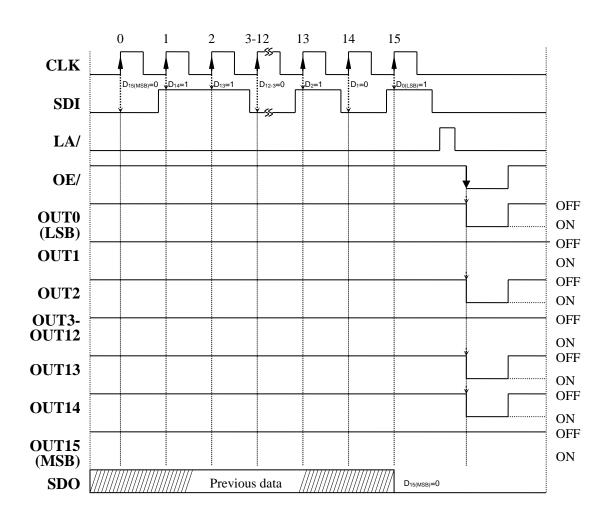

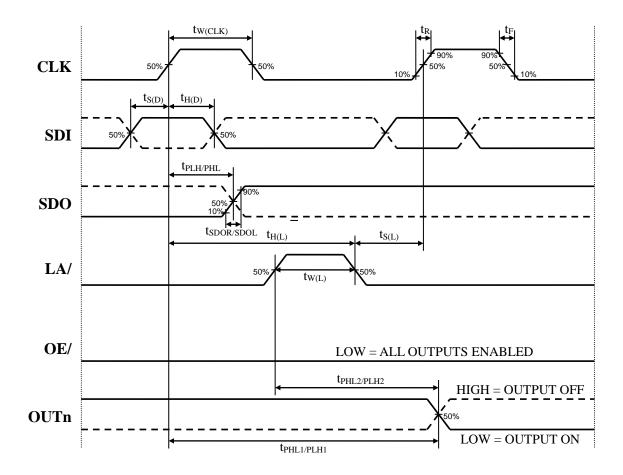

#### **Timing Diagram**

## **Maximum Ratings** (T<sub>A</sub> = 25°C)

| Characte                       | ristic     | Symbol               | Rating                       | Unit       |

|--------------------------------|------------|----------------------|------------------------------|------------|

| Supply voltage                 |            | V <sub>DD</sub>      | 7.0                          | V          |

| Input voltage                  |            | VIN                  | -0.2 to V <sub>DD</sub> +0.2 | V          |

| Output current                 |            | Іоит                 | 60                           | mA/Channel |

| Output valtage                 | SDO        |                      | -0.2 to V <sub>DD</sub> +0.2 | V          |

| Output voltage                 | OUT0~OUT15 | V <sub>оит</sub>     | -0.2 to 17                   | V          |

| Total GND terminals curr       | ent        | IGND                 | 960                          | mA         |

|                                | SOP24      |                      | 1.92                         |            |

| Dawer discination              | SSOP24     |                      | 1.42                         | 10/        |

| Power dissipation              | SSOP24-1.0 | - P <sub>D</sub>     | 1.74                         | W          |

|                                | TQFN24     |                      | 2.08                         |            |

|                                | SOP24      |                      | 65                           |            |

| The was all we sie to be a     | SSOP24     |                      | 88                           | 9C AM      |

| Thermal resistance             | SSOP24-1.0 | R <sub>TH(j-a)</sub> | 72                           | °C /W      |

|                                | TQFN24     | 1                    | 60                           |            |

| Operating junction temperature |            | T <sub>J(max)</sub>  | 150                          | °C         |

| Operating temperature          |            | Topr                 | -40 to +85                   | °C         |

| Storage temperature            |            | T <sub>STG</sub>     | -55 to +150                  | °C         |

The absolute maximum ratings are a set of ratings not to be exceeded. Stresses beyond those listed under "Maximum Ratings" may cause the device breakdown, deterioration even permanent damage. Exposure to the maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions** (T<sub>A=</sub> -40 to 85°C unless otherwise noted)

| Characteristic Symb |                    | Conditions               | Min.               | Тур.       | Max.               | Unit |

|---------------------|--------------------|--------------------------|--------------------|------------|--------------------|------|

| Supply voltage      | $V_{DD}$           | -                        | 3                  | -          | 5.5                | V    |

| Output voltage      | \/                 | Output OFF               | -                  | -          | 17                 | V    |

|                     | Vouт               | Output ON                | -                  | <b>1</b> 1 | 42                 | V    |

| Output current      | Іоит               | V <sub>DD</sub> =3.3/5V  | 2                  | -          | 30/45              | mA   |

| Input voltage       | ViH                | Input signals            | 0.7V <sub>DD</sub> | -          | $V_{DD}$           | V    |

| Input voltage       | VIL                | Input signals            | 0                  | -          | 0.3V <sub>DD</sub> | V    |

| OE/ pulse width     | t <sub>W(OE)</sub> | V <sub>DD</sub> =3.3V/5V | 40                 | -          | -                  | ns   |

The output current keep constant in range of 5-45mA if V<sub>OUT</sub>=1V.

However, user can minimize V<sub>OUT</sub> to reduce power dissipation according to used current, e.g., set V<sub>OUT</sub> to 0.6V if I<sub>OUT</sub>=20mA.

<sup>2.</sup> The maximum Vout is package thermal limited, user should keep Vout under maximum power dissipation.

# **Electrical Characteristics** (V<sub>DD</sub>=3.3/5V, T<sub>A</sub>=25°C unless otherwise noted)

| Characteristic                            |         | Symbol                | Conditions                                                                    | Min.                 | Тур. | Max.               | Unit |

|-------------------------------------------|---------|-----------------------|-------------------------------------------------------------------------------|----------------------|------|--------------------|------|

| Input voltage                             |         | V <sub>IH</sub>       | -                                                                             | $0.7V_{DD}$          | -    | $V_{DD}$           | V    |

| Input voltage                             |         | VIL                   | -                                                                             | 0                    | -    | 0.3V <sub>DD</sub> | V    |

| SDO output volte                          | 200     | Vон                   | $V_{DD}=3.3/5V$ , $I_{OH}=-1mA$                                               | V <sub>DD</sub> -0.4 | -    | -                  | V    |

| SDO output volta                          | age     | Vol                   | $V_{DD}=3.3/5V$ , $I_{OL}=+1mA$                                               | -                    | -    | 0.4                | V    |

| Output leakage of                         | current | lol                   | V <sub>OUT</sub> =17V                                                         | -                    | -    | 0.5                | uA   |

| Output current                            |         | Іоит                  | $V_{OUT}=1V$ , $R_{EXT}=900\Omega$                                            | -                    | 20.5 | -                  | mA   |

| Current bit skew                          | 1       | dl <sub>OUT1</sub>    | $V_{OUT}=1V$ , $R_{EXT}=900\Omega$                                            | -                    | ±1   | ±2                 | %    |

| Chip skew <sup>2</sup>                    |         | dl <sub>OUT2</sub>    | $V_{OUT}=1V$ , $R_{EXT}=900\Omega$                                            | -                    | ±2   | ±3                 | %    |

| Line regulation <sup>3</sup> IOUT VS. VDD |         | %/dV <sub>DD</sub>    | $3V$ < $V$ DD< $5.5V$ , $V$ OUT> $1V$ , $R$ EXT= $900\Omega$                  | -                    | ±0.5 | ±1                 | %/V  |

| Load regulation <sup>4</sup>              |         | %/dV <sub>OUT</sub>   | 1V <v<sub>OUT&lt;4V,<br/>I<sub>OUT</sub>=20.5mA, R<sub>EXT</sub>=900Ω</v<sub> | -                    | ±0.1 | ±0.5               | %/V  |

| Pull-up resistor                          |         | Rup                   | OE/                                                                           | -                    | 400  | -                  | ΚΩ   |

| Pull-down resisto                         | or      | R <sub>DOWN</sub>     | LA/                                                                           | -                    | 400  | -                  | ΚΩ   |

|                                           | OFF     | I <sub>DD(OFF)1</sub> | V <sub>DD</sub> =3.3/5V, R <sub>EXT</sub> =Open,<br>OUT[0:15]=OFF(to VCC)     | -                    | 3    | 4                  |      |

| Supply current                            | OFF     | I <sub>DD(OFF)2</sub> | $V_{DD}$ =3.3/5V, $R_{EXT}$ =900 $\Omega$ , OUT[0:15]=OFF(to VCC)             | -                    | 5    | 7                  | mA   |

|                                           | ON      | I <sub>DD(ON)</sub>   | V <sub>DD</sub> =3.3/5V, R <sub>EXT</sub> =900 Ω,<br>OUT[0:15]=ON             | -                    | 8    | 10                 |      |

- 1. Bit skew= $(I_{OUT}-I_{AVG})/I_{AVG}$ , where  $I_{AVG}=(I_{OUT(max)}+I_{OUT(min)})/2$

- 2. Chip skew= $(I_{AVG}-I_{CEN})/I_{CEN}*100(\%)$ , where  $I_{CEN}$  is the statistics distribution center of output currents.

- $3. \qquad \text{Line regulation=[I_{OUT}(V_{DD}=5.5V)-I_{OUT}(V_{DD}=3V)]} \ I \ \{[I_{OUT}(V_{DD}=5.5V)+I_{OUT}(V_{DD}=3V)]/2\} \ I \ (5.5V-3V)^* \ 100(\%/V) \ I \ (5.5V-3V)^* \ I \ (5.5V-3V)^* \ 100(\%/V) \ I \ (5.5V-3V)^* \$

- $4. \qquad \text{Load regulation=[I_{OUT}(V_{OUT}=4V)-I_{OUT}(V_{OUT}=1V)]} \ I \ \{ [I_{OUT}(V_{OUT}=4V)+I_{OUT}(V_{OUT}=1V)]/2 \} \ I \ (4V-1V)^* 100(\%/V) \\ = 4V 100(\%/V) + 100(\%/V)$

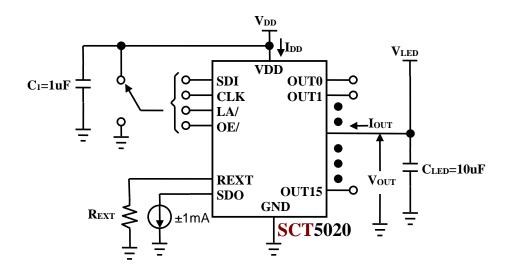

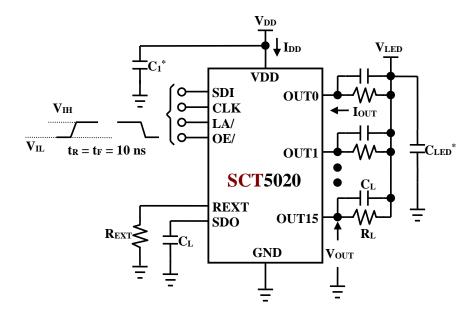

#### **Test Circuit for Electrical Characteristics**

| Characte                        | ristic                   | Symbol                | Conditions                                                 | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------------|-----------------------|------------------------------------------------------------|------|------|------|------|

|                                 | CLK - OUTn               | t <sub>PLH1</sub>     |                                                            | -    | 80   | 150  | ns   |

| Propagation delay               | LA/ - OUTn               | t <sub>PLH2</sub>     |                                                            | -    | 80   | 150  | ns   |

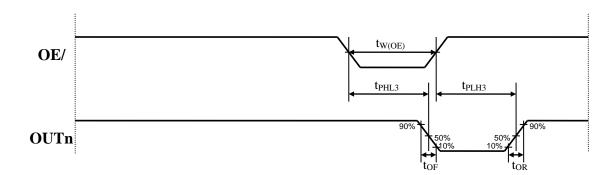

| time ("L" to "H")               | OE/ - OUT0               | t <sub>PLH3</sub>     |                                                            | -    | 80   | 150  | ns   |

|                                 | CLK - SDO                | t <sub>PLH</sub>      |                                                            | -    | 20   | 40   | ns   |

|                                 | CLK - OUTn               | t <sub>PHL1</sub>     |                                                            | -    | 80   | 150  | ns   |

| Propagation delay               | LA/ - OUTn               | t <sub>PHL2</sub>     |                                                            | -    | 80   | 150  | ns   |

| time ("H" to "L")               | OE/ - OUT0               | t <sub>PHL3</sub>     | $V_{DD} = 3.3/5V$                                          | -    | 80   | 150  | ns   |

|                                 | CLK - SDO                | <b>t</b> PHL          | V <sub>LED</sub> = 5V<br>V <sub>IH</sub> = V <sub>DD</sub> | -    | 20   | 40   | ns   |

|                                 | CLK                      | tw(clk)               | V <sub>IL</sub> = GND                                      | 20   | -    | -    | ns   |

| Pulse width                     | LA/                      | t <sub>W(L)</sub>     | $R_{EXT} = 900\Omega$                                      | 20   | -    | -    | ns   |

|                                 | OE/                      | $t_{W(OE)}$           | $R_L = 180\Omega$                                          | 40   | -    | -    | ns   |

| Setup time for SDI              |                          | t <sub>S(D)</sub>     | C <sub>L</sub> = 10pF<br>C <sub>1</sub> = 1uF              | 5    | -    | -    | ns   |

| Hold time for SDI               |                          | t <sub>HD)</sub>      | C <sub>LED</sub> = 10uF                                    | 15   |      |      | ns   |

| Setup time for LA/              |                          | t <sub>S(L)</sub>     |                                                            | 5    | -    | -    | ns   |

| Hold time for LA/               |                          | t <sub>H(L)</sub>     |                                                            | 5    | -    | -    | ns   |

| SDO rise time                   |                          | tsdor                 |                                                            | -    | 10   | -    | ns   |

| SDO fall time                   |                          | tsdof                 |                                                            | -    | 10   | -    | ns   |

| Output rise time of IOUT        |                          | tor                   |                                                            | -    | 40   | 60   | ns   |

| Output fall time of Ic          | Dutput fall time of louт |                       |                                                            | -    | 40   | 60   | ns   |

| Slow CLK rise time <sup>1</sup> |                          | <b>t</b> <sub>R</sub> | Cascade                                                    | -    | -    | 500  | ns   |

| Slow CLK fall time              |                          | t <sub>F</sub>        | Cascade                                                    | -    | -    | 500  | ns   |

# **Test Circuit for Switching Characteristics**

# **Timing Waveform**

#### **LA/ Control Output**

#### **OE/ Control Output**

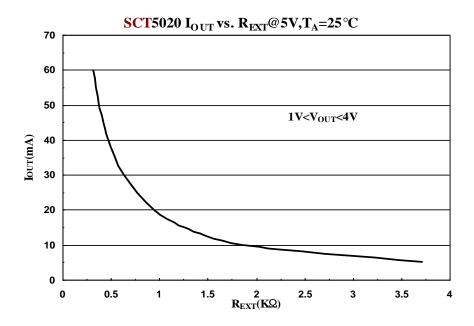

#### **Adjusting Output Current**

The SCT5020's output current (I<sub>OUT</sub>) are set by one external resistor at pin REXT. The output current I<sub>OUT</sub> versus resistance of R<sub>EXT</sub> is shown as the following figure.

According to I-V curve of the output of SCT5020, the output voltage should be larger than 1V to get 45 mA constant current. By applying proper output voltage, the output current set by an external resistor is approximate to:  $I_{OUT} = 30(615 / REXT)$  (mA) (chip skew <  $\pm 3\%$ ). Thus the output current is set to be about 20.5mA at REXT =  $900\Omega$ .

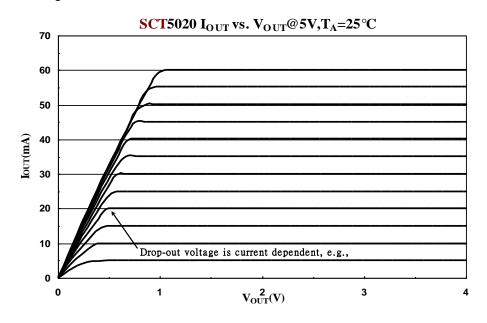

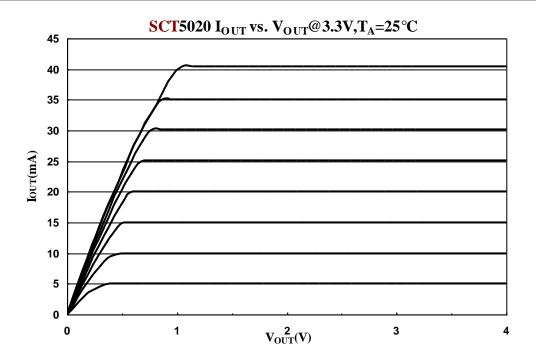

#### **Output Characteristics**

The current characteristic of output curve is flat. The output current can be kept constant regardless of the variations of LED forward voltage when  $V_{\text{OUT}} > V_{\text{DO}}$  (Drop-Out voltage). The relationship between  $I_{\text{OUT}}$  and  $V_{\text{OUT}}$  is shown below. The output voltage should be kept as low as possible to prevent the SCT5020 from being overheated.

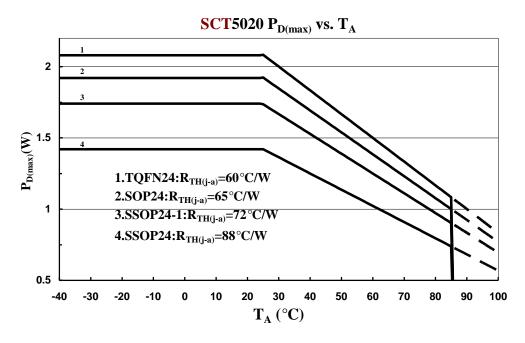

#### **Power Dissipation**

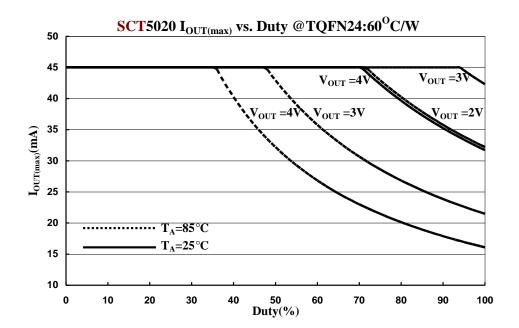

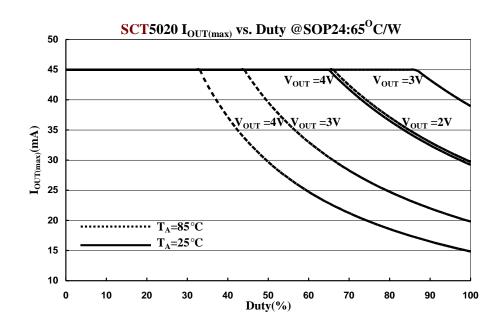

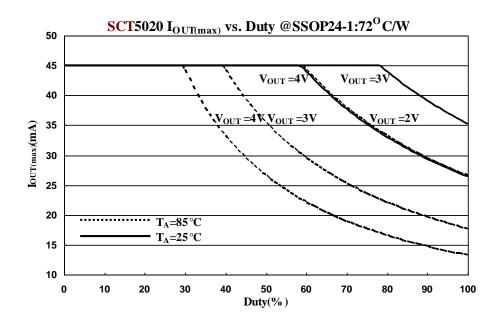

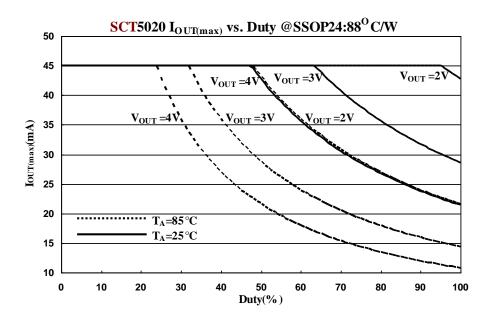

The maximum power dissipation ( $P_{D(max)}$ ) of a semiconductor chip varies with different packages and ambient temperature. It's determined as  $P_{D(max)}=(T_{J(max)}-T_A)/R_{TH(j-a)}$  where  $T_{J(max)}$ : maximum chip junction temperature is usually considered as 150°C,  $T_A$ : ambient temperature,  $R_{TH(j-a)}$ : thermal resistance. Since P=IV, for sinking larger  $I_{OUT}$ , users had better add proper voltage reducers on outputs to reduce the heat generated from the SCT5020.

#### **Limitation on Maximum Output Current**

The maximum output current vs. duty cycle is estimated by:  $I_{OUT(max)} = (((T_{J(max)} - T_A)/R_{TH(j-a)}) - (V_{DD}*I_{DD}))/V_{OUT}/Duty/N \text{ where } T_{J(max)} = 150^{\circ}\text{C}, \text{ N=16(all ON)}$

#### **Load Supply Voltage (V.ED)**

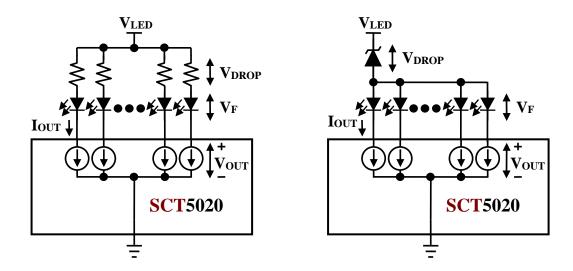

The SCT5020 can be operated very well when V<sub>OUT</sub> ranges from 1V to 4V. However, it is recommended to use the lowest possible supply voltage or set a voltage reducer to reduce the V<sub>OUT</sub> voltage, at the same time reduce the power dissipation of the SCT5020. Suggested V<sub>OUT</sub> is to be set greater than V<sub>DO</sub> and less than 1V. The V<sub>DO</sub> is dependent on the I<sub>OUT</sub> current as indicated in section "Output Characteristics". Follow the diagram instructions shown below to lower down the output voltage. This can be done by adding additional resistor or zener diode, thus V<sub>OUT</sub>=V<sub>LED</sub>-V<sub>DROP</sub>-V<sub>F</sub>.

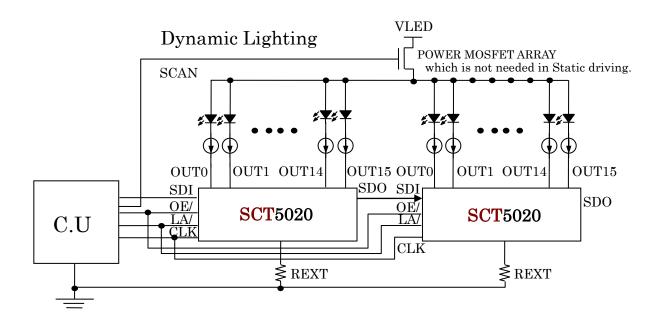

## **Typical Application Circuits**

#### **PCB Design Considerations**

Use the following general guide-line when designing printed circuit boards (PCB):

#### **Decoupling Capacitor**

Place a decoupling capacitor e.g. 1uF between VDD and GND pins of SCT5020. Locate the capacitor as close to the SCT5020 as possible. This is normally adequate for static LED driving. For dynamic scan or PWM applications, it is suggested to add an additional capacitor of 0.1uF or more to each supply for every SCT5020. The necessary capacitance depends on the LED load current, PWM switching frequency, and serial-in data speed. Inadequate VDD decoupling can cause timing problems, and very noisy LED supplies can affect LED current regulation.

#### External Resistor (Rext)

Locate the external resistor as close to the REXT pin as possible to avoid the noise influence.

#### **Power and Ground**

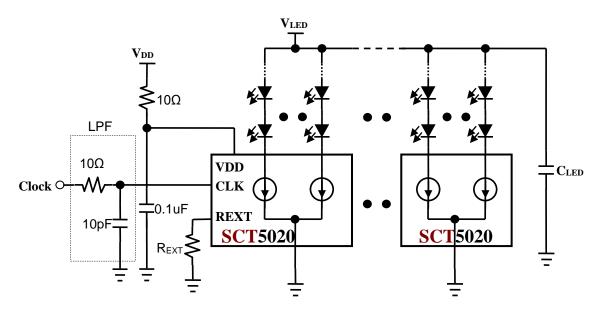

Maximizing the width and minimizing the length of VDD and GND trace improves efficiency and ground bouncing by effect of reducing both power and ground parasitic resistance and inductance. A small value of resistor, e.g.,  $10\Omega$  (higher if  $I_{OUT}$  is larger) series in power input of the SCT5020 in conjunction with decoupling capacitor shunting the IC is recommended. Separating and feeding the LED power from another stable supply terminal  $V_{LED}$ . Furthermore, adding a capacitor  $C_{LED}$  greater than 10uF at  $V_{LED}$  is recommended.

#### **EMI Reduction**

To reduce the EMI radiation from system, an economical solution of RC low pass filter (LPF) is suggested to be used to lower the transient edge of clock input signal, as shown in the figure above. Using at least four layers PCB board with two interior power and ground planes is a good scheme to decrease the signal current path which is the source of radiation emission. As a result, EMI radiation can be decreased.

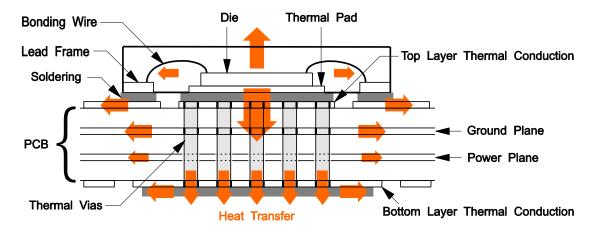

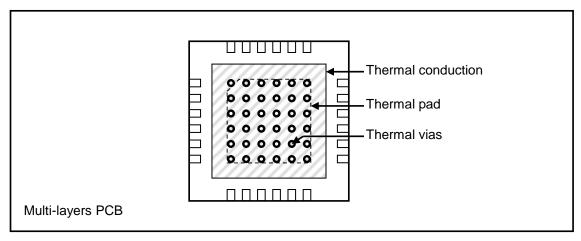

#### **Thermal Pad Consideration**

The "thermal pad" (also named as "exposed pad") TQFN package beneath used to increase the heat dissipation capability is grounded. User should be aware of this electrical connection when designing the PCB board, and make provisions for its use. In most of application, the thermal pad is electrically connected to ground plane or conduction. This makes the IC operated with more stable condition.

In general, the heat generated from an IC is conducted to the PCB then radiates to the ambient. Thermal pad specifically increases the maximum power dissipation capability of the IC packages. To provide lower thermal resistance from the IC to the ambient air, PCB designers should layout larger thermal conduction areas on top layer (component side) and bottom layer (solder side) as well as thermal vias, the more the better. In addition, connecting thermal via to the ground plane also increases thermal conduction areas, this improves the heat transfer efficiency at the same time greatly dissipates heat generated from the package. Furthermore, coating solder on bottom layer and selecting, e.g., 2 oz. copper which will increase the total thickness of thermal conduction is an alternative.

When making the solder paste screen, an opening should be created for the thermal pad. This way the thermal pad can be electrically and thermally connected to the PCB. As the thermal pad is soldered on copper polygon, the chance of inadvertently shorting the thermal pad to traces routed underneath it could be eliminated.

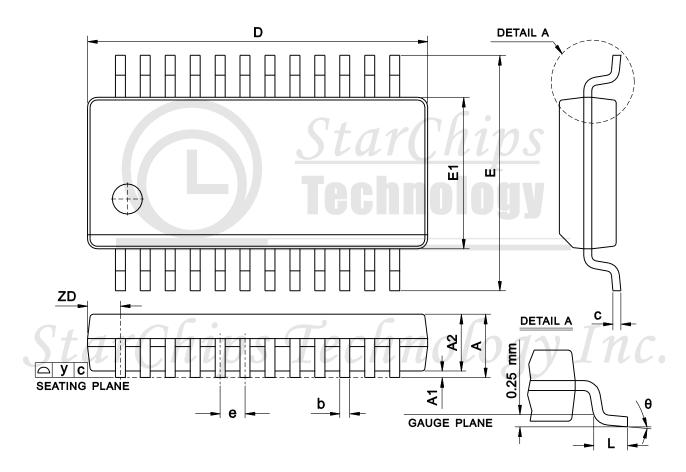

# **Package Dimension**

SSOP24(<u>check up-to-date version</u>)

| Symbol   | D        | imension (mr | n)   | Dimension (mil) |       |       |  |

|----------|----------|--------------|------|-----------------|-------|-------|--|

| Syllibol | Min.     | Nom.         | Max. | Min.            | Nom.  | Max.  |  |

| А        | 1.35     | 1.63         | 1.75 | 53.1            | 64.2  | 68.9  |  |

| A1       | 0.10     | 0.15         | 0.25 | 3.9             | 5.9   | 9.8   |  |

| A2       | -        | -            | 1.50 | -               | -     | 59.1  |  |

| b        | 0.20     | -            | 0.30 | 7.9             | -     | 11.8  |  |

| С        | 0.18     | -            | 0.25 | 7.1             | -     | 9.8   |  |

| D        | 8.56     | 8.66         | 8.74 | 337.0           | 340.9 | 344.1 |  |

| Е        | 5.79     | 5.99         | 6.20 | 228.0           | 235.8 | 244.1 |  |

| E1       | 3.81     | 3.91         | 3.99 | 150.0           | 153.9 | 157.1 |  |

| е        |          | 0.64 BSC     |      | 25.0 BSC        |       |       |  |

| L        | 0.41     | 0.64         | 1.27 | 16.1            | 25.0  | 50.0  |  |

| у        | -        | -            | 0.10 | -               | -     | 3.9   |  |

| ZD       | 0.84 REF |              |      | 33.0 REF        |       |       |  |

| θ        | 0°       | -            | 8°   | 0°              | -     | 8°    |  |

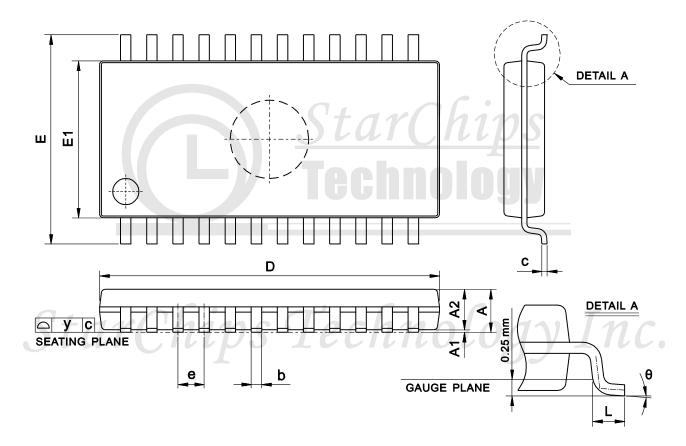

#### SSOP24-1 (check up-to-date version)

| Symbol   | D     | imension (mr | n)    | Dimension (mil) |          |       |  |

|----------|-------|--------------|-------|-----------------|----------|-------|--|

| Syllibol | Min.  | Nom.         | Max.  | Min.            | Nom.     | Max.  |  |

| Α        | -     | -            | 1.90  | -               | -        | 74.8  |  |

| A1       | 0.05  | 0.10         | 0.15  | 2.0             | 3.9      | 5.9   |  |

| A2       | 1.30  | 1.50         | 1.70  | 51.2            | 59.1     | 66.9  |  |

| b        | 0.30  | 0.40         | 0.52  | 11.8            | 15.7     | 20.5  |  |

| С        | 0.10  | 0.15         | 0.27  | 3.9             | 5.9      | 10.6  |  |

| D        | 12.80 | 13.00        | 13.20 | 503.9           | 511.8    | 519.7 |  |

| E        | 7.70  | 8.00         | 8.30  | 303.1           | 315.0    | 326.8 |  |

| E1       | 5.80  | 6.00         | 6.20  | 228.3           | 236.2    | 244.1 |  |

| е        |       | 1.00 BSC     |       |                 | 39.4 BSC |       |  |

| L        | 0.25  | 0.45         | 0.65  | 9.8             | 17.7     | 25.6  |  |

| у        | -     | -            | 0.10  | -               | -        | 3.9   |  |

| θ        | 0°    | -            | 10°   | 0°              | -        | 10°   |  |

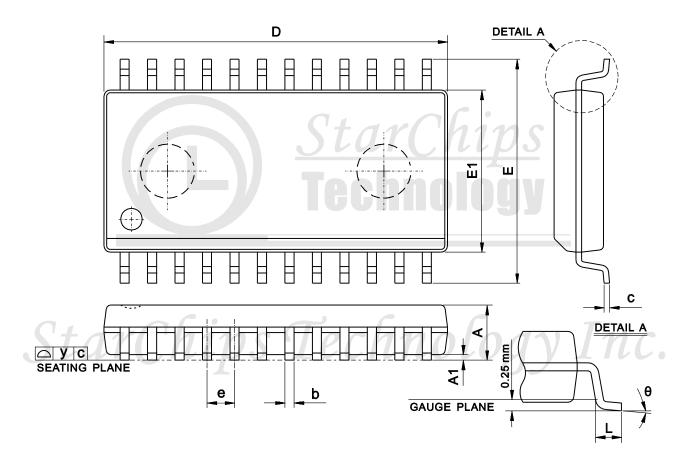

#### SOP24 (check up-to-date version)

| Symbol | D     | imension (mr | n)    | Dimension (mil) |      |       |  |

|--------|-------|--------------|-------|-----------------|------|-------|--|

| Symbol | Min.  | Nom.         | Max.  | Min.            | Nom. | Max.  |  |

| Α      | 2.35  | -            | 2.65  | 92.5            | -    | 104.3 |  |

| A1     | 0.10  | -            | 0.30  | 3.9             | -    | 11.8  |  |

| b      | 0.33  | -            | 0.51  | 13.0            | -    | 20.1  |  |

| С      | 0.23  | -            | 0.32  | 9.1             | -    | 12.6  |  |

| D      | 15.20 | -            | 15.60 | 598.4           | -    | 614.2 |  |

| E      | 10.00 | -            | 10.65 | 393.7           | -    | 419.3 |  |

| E1     | 7.40  | -            | 7.60  | 291.3           | -    | 299.2 |  |

| е      |       | 1.27 BSC     |       | 50.0 BSC        |      |       |  |

| L      | 0.40  | -            | 1.27  | 15.7            | -    | 50.0  |  |

| θ      | 0°    | -            | 8°    | 0°              | -    | 8°    |  |

| у      | -     | -            | 0.10  | -               | -    | 3.9   |  |

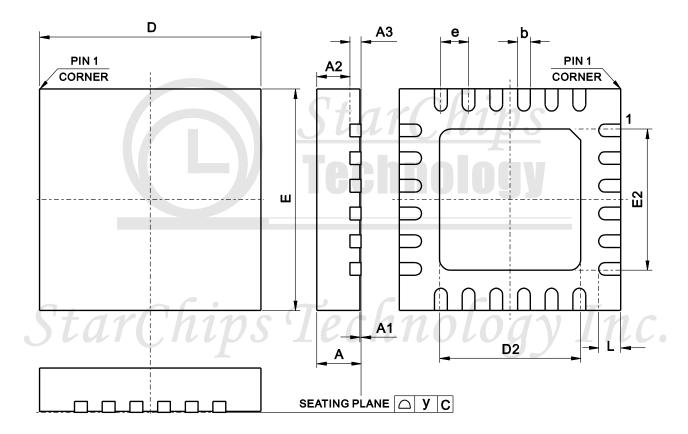

## TQFN24-4x4(CQNG) (check up-to-date version)

| Symbol   | D        | imension (mr | n)   | Dimension (mil) |          |       |  |

|----------|----------|--------------|------|-----------------|----------|-------|--|

| Syllibol | Min.     | Nom.         | Max. | Min.            | Nom.     | Max.  |  |

| А        | 0.76     | 0.80         | 0.84 | 30.0            | 31.0     | 33.0  |  |

| A1       | 0.00     | 0.02         | 0.04 | 0.0             | 0.8      | 1.5   |  |

| A2       | 0.57     | 0.60         | 0.63 | 22.0            | 24.0     | 25.0  |  |

| A3       |          | 0.20 REF     |      |                 | 8.0 REF  |       |  |

| b        | 0.18     | 0.25         | 0.30 | 7.1             | 9.8      | 11.8  |  |

| D        | 3.90     | 4.00         | 4.10 | 154.0           | 157.0    | 161.0 |  |

| D2       | 2.50     | 2.55         | 2.60 | 98.4            | 100.4    | 102.4 |  |

| E        | 3.90     | 4.00         | 4.10 | 154.0           | 157.0    | 161.0 |  |

| E2       | 2.50     | 2.55         | 2.60 | 98.4            | 100.4    | 102.4 |  |

| е        | 0.50 BSC |              |      |                 | 19.7 BSC |       |  |

| Ĺ        | 0.35     | 0.40         | 0.45 | 13.8            | 15.7     | 17.7  |  |

| у        | -        | 0.08         | -    | -               | 3.1      | -     |  |

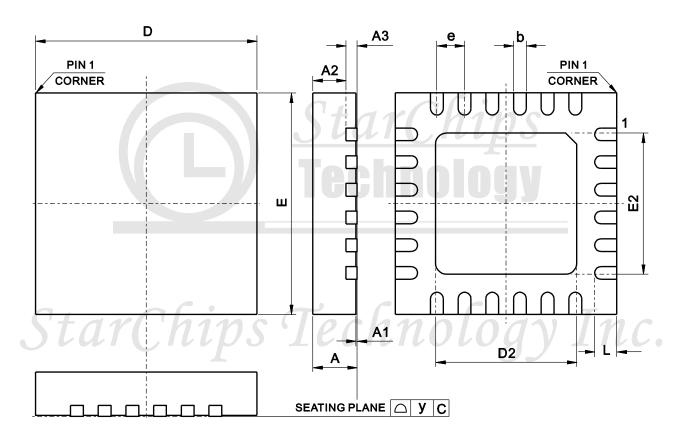

## TQFN24-4x4(AQNG) (check up-to-date version)

| Cumbal | Dimension (mm) |           |      | Dimension (mil) |           |       |  |

|--------|----------------|-----------|------|-----------------|-----------|-------|--|

| Symbol | Min.           | Nom.      | Max. | Min.            | Nom.      | Max.  |  |

| Α      | 0.70           | 0.75      | 0.80 | 27.6            | 29.5      | 31.5  |  |

| A1     | 0.00           | 0.035     | 0.05 | 0.0             | 1.4       | 2.0   |  |

| A2     | -              | 0.55      | 0.57 | -               | 21.7      | 22.4  |  |

| A3     |                | 0.203 REF |      |                 | 8.0 REF   |       |  |

| b      | 0.20           | 0.25      | 0.30 | 7.9             | 9.8       | 11.8  |  |

| D      |                | 4.00 BSC  |      |                 | 157.0 BSC |       |  |

| D2     | 2.40           | 2.50      | 2.60 | 94.5            | 98.4      | 102.4 |  |

| E      | 4.00 BSC       |           |      | 157.0 BSC       |           |       |  |

| E2     | 2.40           | 2.50      | 2.60 | 94.5            | 98.4      | 102.4 |  |

| е      | 0.50 BSC       |           |      | 19.7 BSC        |           |       |  |

| L      | 0.35           | 0.40      | 0.45 | 13.8            | 15.7      | 17.7  |  |

| У      | -              | 0.08      | -    | -               | 3.1       | -     |  |

# **Revision History**(check up-to-date version)

| Data Sheet Version | Remark         |

|--------------------|----------------|

| V01 01             | First released |

Information provided by StarChips Technology is believed to be accurate and reliable. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Starchips can not assume responsibility and any problem raising out of the use of the circuits. Starchips reserves the right to change product specification without prior notice.

StarChips Technology Inc. \_\_\_\_\_www.starchips.com.tw